Предлагаю Вам совершенно вольный перевод на русский язык некоторых страниц технической документации (datasheet) микроконтроллера ATMEL® AVR® ATtiny88.

Характеристики ATtiny88

- Высокопроизводительный 8-разрядный Микроконтроллер AVR® с низким энергопотреблением.

- Усовершенствованная RISC архитектура:

- 123 ассемблерных команды, большинств выполняется за одиночных такт.

- 32 x 8-ми битных рабочих регистра общего назначения.

- Полностью статическое функционирование.

- Сегменты памяти:

- 8 кБайт встроенной самопрограммируемой флэш-памяти.

- 64 байта энергонезависимой EEPROM памяти.

- 512 Байт встроенной SRAM памяти.

- Циклы записи/стирания:

- 10 000 флэш-памяти

- 100 000 EEPROM

- Хранение данных:

- 20 лет при 85°C

- 100 лет при 25°C

- Блокировка несанкционированного копирования программного обеспечения.

- Периферия:

- Один 8-разрядный таймер/счетчик с отдельным пред делителем частоты и режимом сравнения.

- Один 16-разрядный таймер/счетчик с пред делителем частоты и режимами сравнения и захвата.

- 8-ми канальный 10-ти разрядный АЦП (TQFP32)

- Master/Slave последовательный SPI интерфейс

- Байт-ориентированный 2-проводной последовательный интерфейс (Совместим с Philips I2C)

- Программируемый сторожевой таймер с отдельным встроенным генератором (Watchdog)

- Встроенный аналоговый компаратор

- Прерывание и пробуждение при смене состояния входов

- Специальные функции микроконтроллера

- Встроенный внутрисхемный отладчик

- Внутрисхемное программирование через SPI порт.

- RESET при включении программируемое обнаружение пониженного напряжения питания (Brown-Out Detection)

- Внутренний калиброванный генератор

- Внешние и внутренние источники прерываний

- Три режима сна:

- Холостой ход

- шумоподавление АЦП

- отключение питания

- Встроенный датчик температуры

- 28 I/O портов в корпусе TQFP32

- Рабочее Напряжение 1,8 – 5,5 В

- Диапазон рабочих температур от -40 ° C до +85 ° C

- Рабочая частота:

- 0 – 4 МГц при 1,8 – 5,5 В

- 0-8 МГц при 2,7 – 5,5 В

- 0-12 МГц при 4,5 – 5,5 В

- Низкое Энергопотребление

- Активный режим: 1 МГц, 1,8 В: 240 мкА

- Режим отключения питания: 0,1 мкА при 1,8 В

Цоколёвка ATtiny88

Рис.1 ATtiny88 в корпусе TQFP32

На рисунке 1 цветом выделены названия ножек (pin) в терминах Arduino.

1.1. Описание выводов

| Выводы | Назначение |

|---|---|

| VCC | Плюс источника питания |

| AVCC | Вывод напряжения питания для аналого-цифрового преобразователя и выбор ножек портов ввода-вывода. Этот вывод должен быть внешне подключен к VCC, даже если АЦП не используется. Если используется АЦП, рекомендуется, чтобы этот вывод был подключен к VCC через фильтр нижних частот. Следующие контакты получают напряжение питания от AVCC: PC7, PC[5:0] и PA[1:0]. Все остальные ножки портов ввода/вывода получают напряжение питания от VCC. |

| GND | Общий провод. Подключается к минусу источника питания. |

| Port A, B, С | Все порты ввода/вывода микроконтроллера двунаправленные, имеют внутренние подтягивающие резисторы которые выбираются для каждого бита и подключаются к VCC. Когда подключены внутренние подтягивающие резисторы, при подаче низкого уровня сигнала на вход порта ввода/вывода будет протекать входной ток. Выходные буферы портов ввода/вывода имеют симметричные характеристики как на вход так и на выход тока. |

| Port A (PA3:0) | 4-разрядный. |

| Port B (PB7:0) | 8-разрядный. В зависимости от настроек фьюзов выбора тактовой частоты, PB6 может использоваться в качестве входа сигнала для внутренней схемы управления тактовой частотой. |

| Port C (PC7, PC5:0) | 8-разрядный. |

| PC6/RESET | Электрические характеристики PC6 отличаются от характеристик других выводов порта C. Если бит RSTDISBL фьюзов установлен, PC6 используется в качестве порта ввода-вывода, в противном случае, в качестве входа сброса. Низкий уровень на этом выводе приведет к сбросу. |

| Port D (PD7:0) |

8-разрядный. Выходные буферы PD[7:4] имеют симметричные характеристики как и у других портов. Выходные буферы PD[3:0] обладают повышенной нагрузочной способностью при низком уровне на выходе (VOL, sink). |

2. Обзор ATtiny88

ATtiny88 - это 8-ми разрядный микроконтроллер изготовленный по КМОП (CMOS) технологии с низким энергопотреблением, основанный на улучшенной RISC архитектуре AVR. Выполняя мощные инструкции за один такт, ATtiny88 достигает пропускной способности, приближающейся к 1 MIPS/МГц.

ATtiny88 использует следующие режимы для экономии электроэнергии:

- Режим ожидания: останавливает процессор, позволяя таймеру/счетчику, АЦП, аналоговому компаратору, SPI, TWI и системе прерываний продолжать работать.

- Режим шумоподавления АЦП: минимизирует шум переключения во время преобразования АЦП за счет остановки процессора и всех модулей ввода-вывода, кроме АЦП.

- Режим отключения питания: регистры сохраняют свое содержимое, все функции микросхемы отключены до следующего прерывания или аппаратного сброса.

Устройство изготовлено с использованием технологии энергонезависимой памяти высокой плотности Atmel. Встроенная флэш-память ISP позволяет перепрограммировать память программ в системе через последовательный интерфейс SPI, с помощью обычного программатора энергонезависимой памяти или с помощью встроенного загрузчика-программ, работающего на ядре AVR. Загрузочная программа может использовать любой интерфейс для загрузки

прикладной программы во флэш-память. Объединяя 8-разрядный процессор RISC с встроенной само программируемой флэш-памятью на монолитном чипе, Atmel ATtiny88 представляет собой мощный микроконтроллер, который обеспечивает очень гибкое и экономичное решение для многих встроенных приложений управления.

AVR ATtiny88 поддерживается полным набором инструментов для разработки программ и систем, включая компиляторы C, макроассемблеры, отладчики/симуляторы программ и оценочные наборы.

2.1 Блок-схема ATtiny88

Рис. 2. Блок-схема ATtiny88.

Ядро AVR сочетает в себе богатый набор инструкций с 32 рабочими регистрами общего назначения. Все 32 регистра напрямую подключены к арифметико-логическому блоку (ALU), что позволяет получить доступ к двум независимым регистрам в одной инструкции, выполняемой за один такт. Такая архитектура более эффективна в коде и обеспечивает при этом пропускную способность в десять раз лучше, чем у обычных микроконтроллеров CISC.

4. Ядро процессора AVR

В этом разделе обсуждается архитектура ядра AVR в целом. Основная функция ядра процессора заключается в обеспечении правильного выполнения программы. Поэтому центральный процессор должен иметь возможность доступа к памяти, выполнять вычисления, управлять периферийными устройствами и обрабатывать прерывания.

Рис. 3. Блок-схема AVR архитектуры.

Для достижения максимальной производительности и параллелизма, AVR использует Гарвардскую архитектуру процессора – с раздельной памятью и шинами для программ и данных. Инструкции в памяти программы выполняются с помощью одноуровневой конвейерной обработки. Пока выполняется одна инструкция, следующая инструкция предварительно извлекается из памяти программы. Эта концепция позволяет выполнять инструкции в каждом такте. Память программ представляет собой внутрисистемную перепрограммируемую флэш-память.

Файл регистров быстрого доступа содержит 32 8-разрядных рабочих регистра общего назначения со временем доступа в один такт. Это позволяет арифметическому логическому устройству (ALU) выполнять операции за один цикл. В типичной операции ALU два операнда получают из файла регистров, выполняется операция и результат сохраняется обратно в файле регистров – за один такт.

Шесть из 32-х регистров могут использоваться в качестве трех 16-ти разрядных регистров указателей косвенных адресов для данных. Пространственная адресация – позволяет эффективно вычислять адреса. Один из этих указателей адреса также может использоваться в качестве указателя адреса для поиска таблиц во флэш-памяти программы. Регистрами с дополнительным функционалом являются 16-разрядные регистры X, Y и Z.

ALU поддерживает арифметические и логические операции между регистрами или между константой и регистром. Операции с одним регистром также могут выполняться в ALU. После выполнения арифметической операции обновляется регистр состояния (SREG), чтобы отобразить информацию о результате выполнения операции.

Выполнение программы обеспечивается инструкциями условного и безусловного перехода и вызова подпрограмм способными непосредственно обращаться ко всему адресному пространству памяти программ. Большинство инструкций AVR имеют единый 16-разрядный формат слов, но существуют также инструкции 32-разрядного формата. Фактический набор инструкций варьируется, так как некоторые микроконтроллеры реализуют только часть набора инструкций.

Во время прерываний и вызовов подпрограмм, адрес возврата берётся из счетчика команд (PC) помещается в стек. Стек находится в SRAM памяти общих данных и, следовательно, размер стека ограничен только общим размером SRAM и её использованием в программе. Все пользовательские программы должны инициализировать указатель стека (SP) в процедуре сброса до выполнения подпрограмм или прерываний. Указатель стека (SP) доступен для чтения/записи в пространстве адресов регистров ввода-вывода. К данным SRAM можно легко получить доступ с помощью пяти различных режимов адресации, поддерживаемых архитектурой AVR.

Все области памяти в архитектуре AVR являются линейными и регулярными картами памяти.

Гибкий модуль прерываний имеет свои управляющие регистры в адресном пространстве регистров ввода-вывода и дополнительный глобальный Бит разрешения/запрета прерываний в регистре состояния (SREG). Все прерывания имеют отдельный вектор прерывания в таблице векторов прерываний. Прерывания имеют приоритет в соответствии с номером их вектора прерывания. Чем ниже адрес вектора прерывания, тем выше приоритет.

64 Регистра ввода-вывода обслуживают периферию CPU, это управляющие регистры SPI модуля и другие. Доступ к памяти регистров ввода/вывода можно получить напрямую или по адресу в пространстве данных SRAM. Регистры ввода/вывода располагаются в SRAM сразу за файлом регистров быстрого доступа по адресам 0x20 - 0x5F. Кроме того, в ATtiny88 появились дополнительные регистры ввода-вывода которые занимают адреса с 0x60 до 0xFF в SRAM. В адресном пространстве дополнительных регистров ввода-вывода (0x60 до 0xFF) можно использовать только инструкции ST/STS/STD и LD/LDS/LDD.

4.3 Арифметическое логическое устройство (ALU)

Высокопроизводительный AVR ALU работает напрямую со всеми 32 рабочими регистрами общего назначения. За один такт выполняются арифметические операции между регистрами общего назначения или между регистром и значением непосредственно указанным в инструкции. Операции ALU делятся на три основные категории - арифметические, логические и битовые функции. Некоторые реализации архитектуры также предоставляют мощный умножитель, поддерживающий как знаковое и без знаковое умножение, так и дробный формат.

4.4 Регистр состояния

Регистр состояния содержит информацию о результате последней выполненной арифметической инструкции. Эта информация может использоваться для изменения потока программы для выполнения условных операций. Обратите внимание, что регистр состояния обновляется после всех операций ALU, как указано в Справочнике по набору команд. Во многих случаях это устраняет необходимость использования специальных инструкций сравнения, что приводит к более быстрому и компактному коду.

Регистр состояния не сохраняется автоматически при входе в программу обработки прерывания и не восстанавливается при возврате из прерывания. Это должно выполняться программным обеспечением.

4.5 Файл регистров общего назначения

Файл регистров оптимизирован для расширенного набора команд AVR RISC. Для достижения требуемой производительности и гибкости регистровый файл поддерживает следующие схемы ввода/вывода:

- Один 8-битный операнд и один 8-битный результата

- Два 8-битных операнда и один 8-битный результат

- Два 8-битных операнда и один 16-битный результата

- Один 16-битный операнд и один 16-битный результат

Рис. 4. 32 рабочих регистра общего назначения в CPU.

Как показано на рис. 4, каждому регистру также назначается адрес в памяти данных, отображающий их непосредственно в первые 32 ячейки пользовательского пространства данных. Хотя эта организация памяти не реализована физически в качестве ячеек SRAM, она обеспечивает большую гибкость при доступе к регистрам, поскольку регистры указателей X, Y и Z могут быть настроены для индексации любого регистра в файле регистров.

Регистры R26: R31 имеют некоторые дополнительные функции. Эти регистры представляют собой 16-разрядные адресные указатели для косвенной адресации пространства данных. Три регистра косвенного адреса X, Y и Z определены, как показано на рисунке 4.

В различных режимах адресации эти адресные регистры выполняют функции фиксированного смещения, автоматического увеличения и автоматического уменьшения.

4.6 Указатель стека

Стек, в основном, используется для хранения временных данных, локальных переменных и адресов возврата после прерываний и вызовов подпрограмм. Регистры указателя стека (SPH и SPL) всегда указывают на верхнюю часть стека. Обратите внимание, что стек растёт сверху вниз, увеличивается от старших адресов ячеек памяти к младшим. Это означает, что инструкция PUSH уменьшает, а инструкция POP увеличивает значение указателя стека.

Указатель уменьшается на единицу, когда данные помещаются в стек с помощью инструкции PUSH, и увеличивается на единицу, когда данные снимаются со стека с помощью инструкции POP. Он уменьшается на два, когда адрес возврата помещается в стек вызовом подпрограммы или переходом к подпрограмме обслуживания прерывания, и увеличивается на два, когда адрес возврата снимается со стека при возврате из подпрограммы (инструкция RET ) или при возврате из подпрограммы обслуживания прерывания (инструкция RETI).

Указатель стека AVR обычно реализуется как два 8-битных регистра в файле регистров ввода-вывода.

Указатель стека должен быть установлен так, чтобы он указывал выше области регистров ввода-вывода, минимальное значение - это наименьший адрес SRAM.

4.7 Время выполнения инструкции

В этом разделе описываются общие концепции времени доступа для выполнения инструкций. CPU AVR управляется тактовой частотой clkCPU . clkCPU напрямую генерируется из выбранного источника синхронизации. Внутреннее деление тактовой частоты не используется.

4.8 Сброс и обработка прерываний

AVR использует несколько различных источников прерываний. Эти прерывания вместе с функцией RESET имеют отдельный вектор на область памяти программ. Для разрешения прерываний, всем прерываниям назначаются отдельные биты разрешения, которые должны быть записаны в логическую единицу. Так же, имеется глобальный бит разрешения всех прерываний. Он находится в регистре состояния. В зависимости от значения программного счетчика прерывания могут быть автоматически отключены, если блокирующие биты LB2 или LB1 запрограммированы (установлены в 0). Эта функция повышает безопасность программного обеспечения.

Самые младшие адреса в области памяти программ по умолчанию определены как таблица векторов сброса и прерываний. Таблица векторов также определяет уровни приоритета различных прерываний. Чем ниже адрес, тем выше уровень приоритета. СБРОС имеет наивысший приоритет, затем идет INT0 - запрос внешнего прерывания 0.

При возникновении прерывания I-бит глобального разрешения прерывания сбрасывается, и все прерывания запрещаются. Программное обеспечение пользователя может записать логическую единицу в I-бит, чтобы разрешить вложенные прерывания. Все разрешенные прерывания могут затем прервать текущую программу обработки прерываний. Бит I устанавливается автоматически при выполнении инструкции возврата из прерывания - RETI.

В основном, есть два типа прерываний. Первый тип запускается событием, которое устанавливает флаг прерывания. Для этих прерываний программный счетчик направляется на фактический вектор прерывания, чтобы выполнить процедуру обработки прерывания, и аппаратные средства сбрасывают соответствующий флаг прерывания. Флаги прерывания также могут быть очищены путем записи логической единицы в позицию (позиции) битов флага, которые необходимо очистить. Если условие прерывания возникает, когда соответствующий бит разрешения прерывания сброшен, флаг прерывания будет установлен и запомнен до тех пор, пока прерывание не будет разрешено или флаг не будет сброшен программно. Точно так же, если возникает одно или несколько условий прерывания, пока глобальный Бит разрешения прерываний сброшен, соответствующий флаг(и) прерывания будет установлен и запомнен до тех пор, пока не будет установлен глобальный бит разрешения прерывания, а затем будет выполняться в порядке приоритета.

Второй тип прерываний будет срабатывать, пока присутствует условие прерывания. Эти прерывания не обязательно имеют флаги прерывания. Если условие прерывания исчезнет до того, как прерывание будет разрешено, прерывание не будет запущено.

Когда AVR выходит из прерывания, он всегда возвращается в основную программу и выполняет еще одну инструкцию, прежде чем будет обработано любое ожидающее прерывание.

Обратите внимание, что регистр состояния не сохраняется автоматически при входе в программу обработки прерывания и не восстанавливается при возврате из программы обработки прерывания. Это должно выполняться программным обеспечением.

При использовании инструкции CLI для отключения прерываний прерывания будут немедленно отключены. После инструкции CLI прерывание выполняться не будет, даже если оно происходит одновременно с инструкцией CLI.

При использовании инструкции SEI для разрешения прерываний, инструкция, следующая за SEI, будет выполняться раньше любых ожидающих в очереди прерываний.

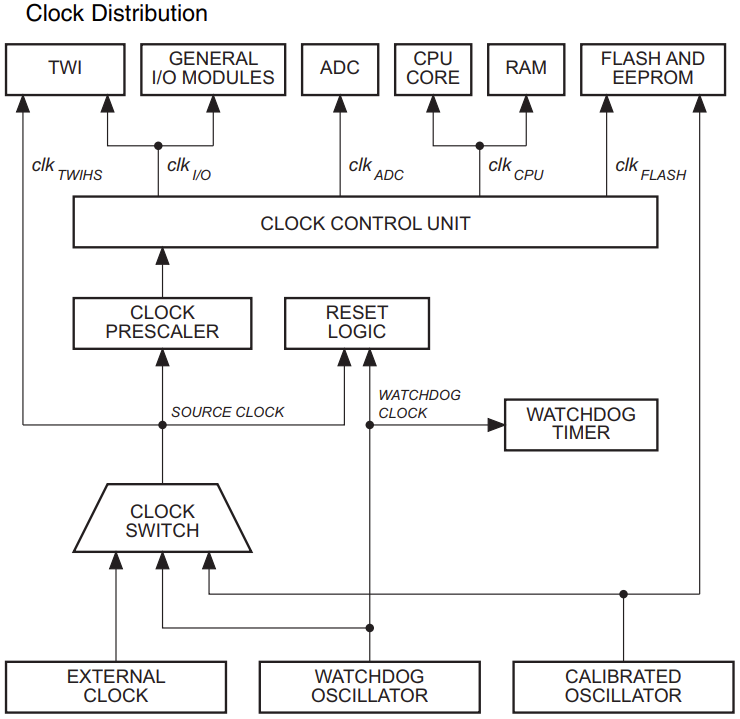

6. Система тактирования

На рисунке 6.1 представлены основные системы тактирования в AVR и их распределение. Все часы тактовые импульсы не обязательно должны быть активными в определенное время. Чтобы снизить энергопотребление, тактовую частоту неиспользуемых модулей можно остановить с помощью различных энергосберегающих режимов (Sleep modes).

Рис. 6.1 Распределение тактовых импульсов.

6.2 Источники тактирования

Микроконтроллер ATtiny88 может использовать любой из следующих источников тактовых импульсов:

| CKSEL[1:0] | Источник тактирования | Допустимая частота |

| 00 | Внешний генератор | 0 – 12 MHz |

| 01 | Резерв | |

| 10 | Калиброванный внутренний генератор | 8.0 MHz |

| 11 | Внутренний генератор | 128 kHz |

Фьюз CKDIV8 можно запрограммировать на деление внутренней частоты 8.0 MHz на 8.

7. Управление электропитанием и режимы энергосбережения микроконтроллера ATtiny88

Энергосберегающие режимы (Sleep modes) позволяют приложению отключать неиспользуемые модули в MCU, тем самым экономя электроэнергию. AVR предоставляет различные энергосберегающие режимы, позволяющие пользователю адаптировать энергопотребление к требованиям приложения.

Когда включен детектор пониженного напряжения (BOD), он активно контролирует напряжение источника питания, в том числе и во время периодов сна. Для дополнительной экономии энергии можно отключить BOD в некоторых режимах пониженного энергопотребления.

7.1 Энергосберегающие режимы

| Режим | Описание | SMCR | Активные источники тактирования | Генератор | Инициаторы выхода из энергосберегающего режима | ||||||||||

| SM1 | SM0 | SE | clkCPU | clkFLASH | clkIO | clkADC | Главный источник тактирования | INT1, INT0 and Pin Change | TWI Address Match | EEPROM Ready | ADC | WDT | other I/O | ||

| Idle | Режим ожидания | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | ||

| ADC Noise Reduction | Шумоподавление АЦП | 0 | 1 | 1 | X | X | X | X | X | X | |||||

| Power-down | Отключение питания | 1 | 0 | 1 | X | X | X | ||||||||

Таблица 7.1 Энергосберегающие режимы, активные источники тактирования, инициаторы пробуждения (выхода из энергосберегающего режима).

Чтобы войти в любой из спящих режимов, бит SE в регистр ввода/вывода SMCR должна быть записана 1 и должна быть выполнена инструкция SLEEP. Битами SM1 и SM0 в регистре SMCR выбирают, какой режим энергосбережения (режим ожидания, шумоподавление АЦП или отключение питания) будет активирован инструкцией SLEEP.

Если разрешенное прерывание происходит, когда микроконтроллер ATtiny88 находится в спящем режиме, микроконтроллер выходит из спящего режима. Затем микроконтроллер останавливается на четыре цикла в дополнение к времени запуска, выполняет процедуру прерывания и возобновляет выполнение с инструкции, следующей за SLEEP. Содержимое регистрового файла и SRAM не изменяется, когда микроконтроллер выходит из спящего режима. Если сброс происходит в спящем режиме, микроконтроллер выходит из спящего режима и запускается с вектора сброса.

Обратите внимание, что если прерывание, инициируемое уровнем, используется для пробуждения, измененный уровень должен удерживаться в течение

некоторого времени, чтобы разбудить микроконтроллер и чтобы микроконтроллер вошёл в процедуру обслуживания прерывания.

7.4.2 MCUCR – регистр управления микроконтроллером

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | BODS | BODSE | PUD | |||||

| Read/Write | R | R/W | R/W | R/W | R | R | R | R |

| Начальное значение | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 6 - BODS должен быть установлен в 1, чтобы разрешить отключение модуля BOD при переходе микроконтроллера в режим энергосбережения. Запись в бит BODS управляется синхронизированной последовательностью записи 1 в бит разрешения BODSE в регистре MCUCR.

- Сначала необходимо установить BODSE в 1.

- Затем, необходимо установить бит BODS в 1

- BODSE должен быть установлен в 0 в течение четырех тактовых циклов

- Бит BODS активен через три тактовых цикла после установки.

- Команда sleep должна выполняться, пока активен BODS

- Бит BODS автоматически очищается после трех тактов

7.4.3 PRR - Регистр снижения энергопотребления

Регистр PRR обеспечивает метод остановки синхронизации отдельных периферийных устройств для снижения энергопотребления. Текущее состояние периферийного устройства замораживается, и регистры ввода-вывода не могут быть прочитаны или записаны. Ресурсы, используемые периферийным устройством при остановке тактирования, останутся занятыми, поэтому в большинстве случаев периферийное устройство должно быть отключено перед остановкой. Пробуждение модуля выполняется сбросом бита в PRR и переводит модуль в то же состояние, что и до выключения.

17. АЦП - аналого-цифровой преобразователь.

Примеры использования: Датчик температуры в ATtiny88,

17.1 Функции АЦП.

- 10-ти битное разрешение

- 1 LSB Интегральная нелинейность

- Абсолютная точность ± 2 младшего разряда

- 14 мкс Время преобразования

- 15 kSPS при максимальном разрешении

- Шесть мультиплексированных односторонних входных каналов

- + Два дополнительных входных канала в корпусах TQFP, QFN и UFBGA с 32 выводами

- + Входной канал датчика температуры

- Дополнительная регулировка влево для считывания результатов АЦП

- 0 - VCC Диапазон входного напряжения АЦП

- Выбираемое опорное напряжение АЦП 1,1 В

- Свободно работающий режим или режим одиночного преобразования

- Прерывание при завершении преобразования АЦП

- Шумоподавитель в спящем режиме

17.2 Обзор.

ATtiny88 оснащен 10-битным аналого-цифровым преобразователем (АЦП) последовательного приближения. АЦП подключен к аналоговому девяти канальному мультиплексору, что позволяет АЦП измерять напряжение на шести или восьми (в зависимости от типа корпуса микроконтроллера) несимметричных входах и от одного внутреннего источника напряжения, поступающего от внутреннего датчика температуры. Напряжение на входах

измеряется относительно 0 В (GND).

АЦП содержит схему выборки и хранения, которая обеспечивает поддержание входного напряжения АЦП на постоянном уровне во время преобразования. Блок-схема АЦП показана в Рисунок 17-1.

Рис. 17.1. Блок-схема АЦП.

Имеется отдельный аналоговый вывод напряжения питания для АЦП, AVCC. Разница напряжений между выводами напряжения питания VCC и AVCC не должна превышать 0,3. Схему подключения аналогового вывода напряжения питания AVCC смотрите на рисунке 17.9.

Внутренний источник опорного напряжение номиналом 1,1 В может быть использован качестве альтернативы VCC.

17.3 Работа

Для использования АЦП, бит снижения мощности PRADC в регистре снижения мощности (PRR) должен быть сброшен.

АЦП преобразует аналоговое входное напряжение в 10-битное цифровое значение путем последовательного приближения. Минимальное значение измеряемого напряжения 0 В на ножке GND микроконтроллера, а максимальное значение измеряемого напряжения равно опорному напряжению. Опорное напряжение АЦП можно выбрать, записав бит REFS0 в регистр ADMUX. Альтернативами являются вывод питания AVCC (REFS0=1) и внутренний источник опорного напряжения 1,1 В (REFS0=0).

Канал аналогового входа выбирается записью в биты MUX в регистре ADMUX. Любой из входных контактов АЦП, а также GND и опорное напряжение с фиксированной шириной запрещенной зоны можно выбрать в качестве несимметричных входов для АЦП.

АЦП включается установкой бита включения АЦП, ADEN в регистре ADCSRA. Выбор опорного напряжения и входного канала не вступит в силу, пока не будет установлен ADEN. АЦП не потребляет электроэнергию, когда ADEN сброшен, поэтому рекомендуется выключить АЦП перед переходом в энергосберегающие спящие режимы.

АЦП генерирует 10-битный результат, который отображается в регистрах данных АЦП, ADCH и ADCL. По умолчанию результат отображается с корректировкой вправо, но при желании может быть представлен с корректировкой влево путем установки бита ADLAR в регистре ADMUX.

Если результат скорректирован и требуется не более 8-битной точности, достаточно прочитать только ADCH. В противном случае сначала необходимо прочитать ADCL, а затем ADCH, чтобы быть уверенным, что содержимое регистров данных принадлежит одному и тому же преобразованию. После чтения регистра ADCL доступ АЦП к регистрам данных блокируется. Это означает, что если ADCL был прочитан и преобразование завершается до того, как ADCH считывается, ни один регистр не изменяется, и результат текущего преобразования теряется. Когда ADCH считывается, доступ АЦП к регистрам ADCH и ADCL снова разрешается.

У АЦП есть собственное прерывание, которое может быть запущено после завершения преобразования. Когда доступ АЦП к регистрам данных запрещен между чтением ADCH и ADCL, прерывание сработает, даже если результат будет потерян.

17.4 Запуск аналогово-цифрового преобразования

Убедитесь что АЦП запитан, очистив бит снижения мощности АЦП PRADC, в регистре снижения мощности PRR.

Одиночное преобразование запускается записью логической единицы в бит ADC Start Conversion (ADSC). Этот бит остается установленным, пока выполняется преобразование, и будет сброшен аппаратными средствами, когда преобразование будет завершено. Если во время преобразования выбран другой канал данных, АЦП завершит текущее преобразование перед выполнением смены канала.

Кроме того, преобразование может запускаться автоматически из различных источников. Автоматический запуск включается установкой бита включения автоматического запуска АЦП, ADATE в регистре ADCSRA. Источник запуска выбирается путем установки битов выбора запуска АЦП, ADTS в регистре ADCSRB (список источников запуска см. В описании битов ADTS). Когда на выбранном источнике запуска возникает положительный фронт, предварительный делитель АЦП сбрасывается и начинается преобразование. Это обеспечивает метод запуска преобразований через фиксированные интервалы. Если сигнал триггера по-прежнему установлен, когда преобразование завершено, новое преобразование запускаться не будет. Если другой положительный фронт появляется на источнике запуска во время преобразования, он будет проигнорирован. Обратите внимание, что флаг прерывания будет установлен, даже если конкретное прерывание отключено или бит разрешения глобального прерывания в SREG сброшен. Таким образом, преобразование может быть запущено без прерывания. Однако флаг прерывания должен быть сброшен, чтобы запустить новое преобразование при следующем событии прерывания.

Рис. 17.2. Логика автоматического запуска АЦП.

Использование флага прерывания АЦП в качестве источника запуска заставляет АЦП начать новое преобразование, как только текущее преобразование завершится. Затем АЦП работает в режиме автономной работы, постоянно осуществляя выборку и обновление регистра данных АЦП. Первое преобразование должно быть начато записью логической единицы в бит ADSC в ADCSRA. В этом режиме АЦП будет выполнять последовательные

преобразования независимо от того, сброшен флаг прерывания АЦП, ADIF или нет.

Если автоматический запуск включен, одиночные преобразования могут быть запущены путем записи ADSC в ADCSRA в единицу. ADSC также можно использовать для определения того, выполняется ли преобразование. Бит ADSC будет считываться как один во время преобразования, независимо от того, как преобразование было начато.

Рис. 17.9. Подключение питания АЦП.

17.5 Делитель частоты и время преобразования

По умолчанию, для получения максимального разрешения, схема последовательного приближения требует входной тактовой частоты от 50 кГц до 200 кГц. Если требуется разрешение меньше чем 10 бит, входная тактовая частота АЦП может быть выше 200 кГц. Это позволяет получить более высокую частоту дискретизации. Но не рекомендуется использовать более высокую тактовую частоту тактового сигнала чем 1 МГц.

Рис. 17.3. Предделитель АЦП.

Модуль АЦП содержит предделитель, как показано на Рисунок 17.3, которые генерируютполучает приемлемую тактовую частоту АЦП от любой частоты процессора выше 100 кГц. Коеффициент деления устанавливается с помощью ADPS битов в регистре ADCSRA. Предварительный делитель начинает отсчет с момента включения АЦП путем установки бита ADEN в регистре ADCSRA. Предварительный делитель продолжает работать до тех пор, пока установлен бит ADEN, и постоянно сбрасывается при низком уровне ADEN.

Когда начинается одиночное преобразование инициированное установкой бита ADSC в регистре ADCSRA, преобразование начинается со следующего нарастающего фронта тактового цикла АЦП.

Обычное преобразование занимает 13 тактов АЦП. Первое преобразование после включения АЦП (ADEN в ADCSRA установлено) занимает 25 тактов АЦП для инициализации аналоговой схемы, как показано на рисунке 17.4.

Рисунок 17-4. Временная диаграмма АЦП, первое преобразование (режим одиночного преобразования).

Фактическая выборка и удержание происходит через 1,5 тактовых цикла АЦП после начала нормального преобразования и 13,5 тактовых циклов АЦП после начала первого преобразования. Когда преобразование завершено, результат записывается в регистры данных АЦП, и устанавливается ADIF. В режиме одиночного преобразования одновременно сбрасывается ADSC. Затем программное обеспечение может снова установить ADSC, и новое

преобразование будет инициировано на первом нарастающем фронте тактовой частоты АЦП.

Рисунок 17-5. Временная диаграмма АЦП, одиночное преобразование.

Когда используется автоматический запуск, предварительный делитель сбрасывается, когда происходит событие запуска, как показано на рисунке 17.6. Это обеспечивает фиксированную задержку от триггерного события до начала преобразования. В этом режиме выборки и хранения выполняется два тактовых цикла АЦП после нарастающего фронта сигнала источника запуска. Для синхронизации логики используются три дополнительных тактовых цикла ЦП.

Рис. 17.6. Временная диаграмма АЦП, автоматическое преобразование.

В режиме произвольного запуска, новое преобразование будет запущено сразу после его завершения, пока ADSC останётся на высоком уровне. Смотрите рисунок 17.7.

Рис. 17-7. Временная диаграмма АЦП произвольного запуска преобразования.

Сводка времени преобразования размещена в таблице 17.1.

Табл. 17-1. Время аналогово-цифрового преобразования.

17.6 Выбор канала или опорного напряжения

Биты MUXn и REFS0 в регистре ADMUX однократно буферизуются через временный регистр, к которому ЦП имеет произвольный доступ. Это гарантирует, что выбор каналов и опорного напряжения будет происходить только в безопасной точке во время преобразования. Выбор канала и опорного напряжения постоянно обновляется, пока не начнется преобразование. После начала преобразования выбор канала и опорного напряжения блокируется, чтобы обеспечить достаточное время выборки для АЦП. Непрерывное обновление возобновляется в последнем тактовом цикле АЦП до завершения преобразования (установлен ADIF в ADC-SRA). Обратите внимание, что преобразование начинается на следующем нарастающем фронте тактовой частоты АЦП после записи ADSC. Таким образом, пользователю рекомендуется не записывать новые значения выбора канала или ссылки в ADMUX до тех пор, пока не будет записан один тактовый цикл АЦП после записи ADSC.

Если используется автоматический запуск, точное время запускающего события может быть неопределенным. Особое внимание должно быть принято при обновлении ADMUX регистра, для того, чтобы контроль, преобразования будет затронуты новыми настройками.

Если и ADATE, и ADEN установлены в 1, событие прерывания может произойти в любое время. Если регистр ADMUX изменяется в этот период, пользователь не может определить, будет ли следующее преобразование основано на старых или новых настройках. ADMUX можно безопасно обновить следующими способами:

- При удалении ADATE или ADEN.

- Во время преобразования минимум один тактовый цикл АЦП после события запуска.

- После преобразования перед сбросом флага прерывания, используемого в качестве источника запуска.

В случае обновления ADMUX при одном из этих условий, новые настройки повлияют на следующее преобразование АЦП.